## Nitrogen Doping of Gallium Oxide by Ion Implantation and Its Application to Vertical Transistors

M. Higashiwaki,<sup>1</sup> M. H. Wong,<sup>1\*</sup> K. Goto,<sup>2</sup> H. Murakami,<sup>2</sup> and Y. Kumagai<sup>2</sup>

<sup>1</sup> National Institute of Information and Communications Technology, Koganei, Tokyo 184-8795, Japan

<sup>2</sup> Department of Applied Chemistry, Tokyo University of Agriculture and Technology, Koganei, Tokyo 184-8588, Japan

<sup>\*</sup> Currently with Department of Electrical and Computer Engineering, University of Massachusetts, Lowell, MA 01854, USA

$\beta$ -gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) has a very large bandgap (~4.5 eV) and a breakdown electric field exceeding 6 MV/cm, making it an attractive candidate for next-generation power electronics. However, Ga<sub>2</sub>O<sub>3</sub> has a fundamental physical drawback, namely a lack of hole-conductive *p*-type material, because of unavailability of shallow acceptors, a valence band structure mostly formed by O 2*p* orbitals, and a self-trapping effect of free holes. Recently, we succeeded in developing a nitrogen (N)-ion-implantation doping process for Ga<sub>2</sub>O<sub>3</sub> to form an energy barrier in a device structure [1] and then fabricating vertical Ga<sub>2</sub>O<sub>3</sub> transistors by using a device process based on the N-ion implantation doping [2, 3].

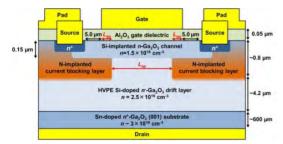

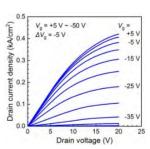

N atoms are theoretically expected to be a deep acceptor in  $Ga_2O_3$ . We performed Nion implantation doping into an *n*- $Ga_2O_3$  layer to fabricate a current blocking layer by forming a Si-doped–N-doped–Si-doped  $Ga_2O_3$  *n-p-n* junction. Note that Si is a shallow donor with an activation energy of about 50 meV in  $Ga_2O_3$ . Then, depletion-mode (Dmode) and enhancement-mode (E-mode) vertical  $Ga_2O_3$  transistors with a current aperture were fabricated by using a manufacturable all-ion-implanted process, which is similar to commercial Si and SiC power device technologies, with Si and N doping. Both the D-mode and E-mode devices demonstrated successful transistor action and decent device characteristics. A schematic cross section and DC current–voltage (*I–V*) output characteristics of a typical D-mode transistor are shown in Figs. 1 and 2, respectively.

This work was partially supported by Council for Science, Technology and Innovation (CSTI), Cross-ministerial Strategic Innovation Promotion Program (SIP), "Next-generation power electronics" (funding agency: NEDO).

Figure 1. Cross-sectional schematic of D-mode vertical Ga<sub>2</sub>O<sub>3</sub> transistor structure:  $L_{ap}$ =20 µm and  $L_{so}$ =2.5 µm.

Figure 2. DC I-V characteristics of D-mode vertical Ga<sub>2</sub>O<sub>3</sub> transistor.

- [1] M. H. Wong, M. Higashiwaki et al., Appl. Phys. Lett. 113, 102103 (2018).

- [2] M. H. Wong, M. Higashiwaki et al., IEEE Electron Device Lett. 40, 431 (2019).

- [3] M. H. Wong, M. Higashiwaki et al., in Abstract of 77th Device Research Conference, 2019.

<sup>&</sup>lt;sup>+</sup> Author for correspondence: mhigashi@nict.go.jp