## Buffer layer growth for III-V on Si substrates using Molecular Beam Epitaxy

<u>Geun-Hwan Ryu</u><sup>1,2</sup>, Jin-Dong Song<sup>2</sup>, Seung-Yeop Ahn<sup>2</sup>, Nam-Gi Hong<sup>2,3</sup>, Han-Youl Ryu<sup>1\*</sup>, Won-Jun Choi<sup>2\*</sup>

<sup>1</sup> Department of Physics, Inha University, Incheon 22212, Korea.

<sup>2</sup> Center for Opto-Electronic materials and Devices, Korea Institute of Science and Technology, Seoul 02792, Korea.

<sup>3</sup> School of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, Korea.

As we approach the physical limits of silicon in the semiconductor industry, there have been many attempts to overcome these obstacles. One of these attempts is to use III-V semiconductors due to its superior physical characteristics. However, epitaxial growth of III-V materials have been limited to III-V substrates such as GaAs and InP. In order to take advantage of Si substrates, which has been used for decades in the semiconductor industry due to its ease of use, low cost, availability in large areas and physical properties such as thermal conductivity, a well-constructed buffer layer is critical for heteroepitaxy of III-V materials. This buffer layer may overcome defects such as threading dislocation and antiphase boundaries which are normally associated with heteroepitaxial growth. Here, we demonstrate the growth of a buffer layer using a seed layer and SPS to minimize defects.

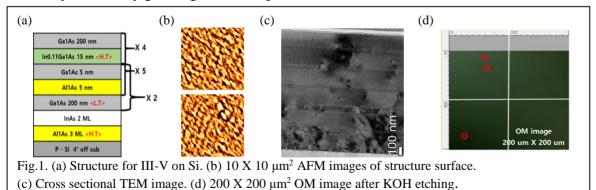

Fig. 1(a) shows the structure of III-V on Si using a seed layer and Short-Period Superlattice (SPS). The AlAs seed layer is grown at a high temperature while the AlAs/GaAs SPS is grown at a low temperature. The buffer layer is terminated by an InGaAs/GaAs Defect Fiter Layer (DFL) structure. The surface roughness measured by Atomic Force Microscopy (AFM) was 2 nm (root mean square) (Fig. 1(b)). Fig. 1(c) shows the cross-section of the buffer layer using Transmission Electron Microscopy (TEM). It is apparent that the surface is improved in AlAs/GaAs SPS and the dislocation is decreased InGaAs/GaAs DFL. Fig. 1(d) shows the result of Etch-Pit Density (EPD) measurement using KOH solution and Optical Microscopy (OM). Average EPD value was 3,000 /cm<sup>2</sup>. As a result, we expect to grow low-cost, high-efficiency devices by growing III-V compound semiconductor on Si substrates.

[1] Di Liang, nature Photonics, 4, 511-517 (2010).

[2] T.Tsuji, Journal of Crystal Growth, 201/202, 1010-1014 (1999)

[3] JinKwan Kwoen, Optics Express, 26, 9, 11568-11576 (2018)

<sup>+</sup> Author for correspondence: wjchoi@kist.re.kr, hanryu@inha.ac.kr