## Nitrogen-Doped SiO<sub>2</sub> Gate Insulator for Enhanced Stability in ALD-IGZO TFTs

<u>Tae-Heon Kim</u>, Dong-Gyu Kim, and Jin-Seong Park <sup>1</sup>Division of Materials Science and Engineering, Hanyang University, 222 Wangsimni-ro, Seongdong-gu, Seoul, Republic of Korea.

AA13: Display Application: Thin Film Transistor, Diodes, Thin Film Encapsulation for OLEDs/QDs...

Silicon nitride  $(SiN_x)$  has gained attention as an insulating layer for oxide thin-film transistors (TFTs) due to its high dielectric constant and density, though its high hydrogen content can degrade device reliability. To address this, silicon oxynitride  $(SiO_xN_y)$  structures have been explored, leveraging the benefits of both  $SiO_2$  and  $SiN_x$  through nitrogen incorporation. Among various doping techniques, atomic layer deposition (ALD) is particularly effective due to its low-temperature process, superior step coverage, and ability to minimize hydrogen-related bonds like Si–OH.

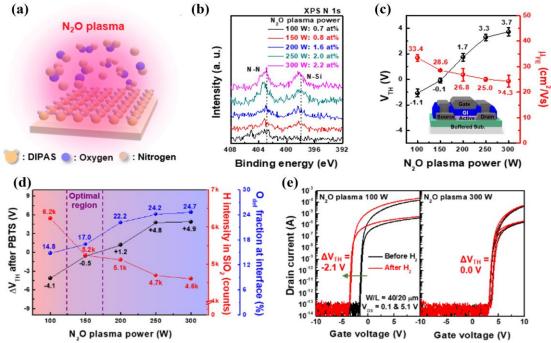

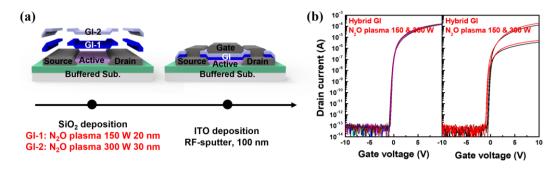

This study proposes a nitrogen doping strategy for SiO<sub>2</sub> gate insulators (GI) using a nitrous oxide (N<sub>2</sub>O) plasma reactant to optimize the active layer/GI interface and bulk properties in top-gate bottom-contact (TG-BC) IGZO TFTs. Increasing N<sub>2</sub>O plasma power from 100 to 300 W raised the nitrogen concentration in SiO<sub>2</sub> from 0.7 to 2.2 at% but also increased trap densities, leading to a U-shaped threshold voltage (V<sub>TH</sub>) shift from -4.1 to 4.9 V under positive bias temperature stress (PBTS). Hydrogen annealing effectively reduced the V<sub>TH</sub> shift from -2.1 to 0.0 V by chemically trapping hydrogen with nitrogen atoms. A hybrid GI structure using N<sub>2</sub>O plasma at 150 and 300 W further improved PBTS stability and hydrogen resistance, highlighting the effectiveness of this approach in enhancing IGZO TFT reliability.

References

[1] IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 69, NO. 6, JUNE 2022[2] IEEE TRANSACTIONS ON ELECTRONDEVICES, VOL. 67, NO. 10, OCTOBER 2020

## Nitrogen-Doped SiO<sub>2</sub> Gate Insulator for Enhanced Stability in ALD-IGZO

## TFTs

<u>Tae-Heon Kim</u>, Dong-Gyu Kim, and Jin-Seong Park <sup>1</sup>Division of Materials Science and Engineering, Hanyang University, 222 Wangsimni-ro, Seongdong-gu, Seoul, Republic of Korea.

Figure1 (a) Schematic of the deposition process for N-doped SiO<sub>2</sub> films using N<sub>2</sub>O plasma. X-ray photoelectron spectroscopy (XPS) spectra of (b) N 1s. (c) V<sub>TH</sub> and  $\mu_{FE}$  variations with N<sub>2</sub>O plasma power during gate insulator (GI) deposition. (d) Variations in  $\Delta V_{TH}$  after PBTS, H intensity in N-doped SiO<sub>2</sub>, and O<sub>def</sub> fraction at the active channel layer. (e) Transfer curves before and after H<sub>2</sub> annealing

Figure 2(a) Schematic of the hybrid GI design consisting of a 20 nm N-doped SiO<sub>2</sub> film deposited with 150 (GI-1) and 300 W (GI-2)  $N_2O$  plasma power. (b) resistivity with  $H_2$  annealing of devices